# SHARP

# LM32K10 Passive Matrix Color LCD

# LCD Data Sheet

# FEATURES

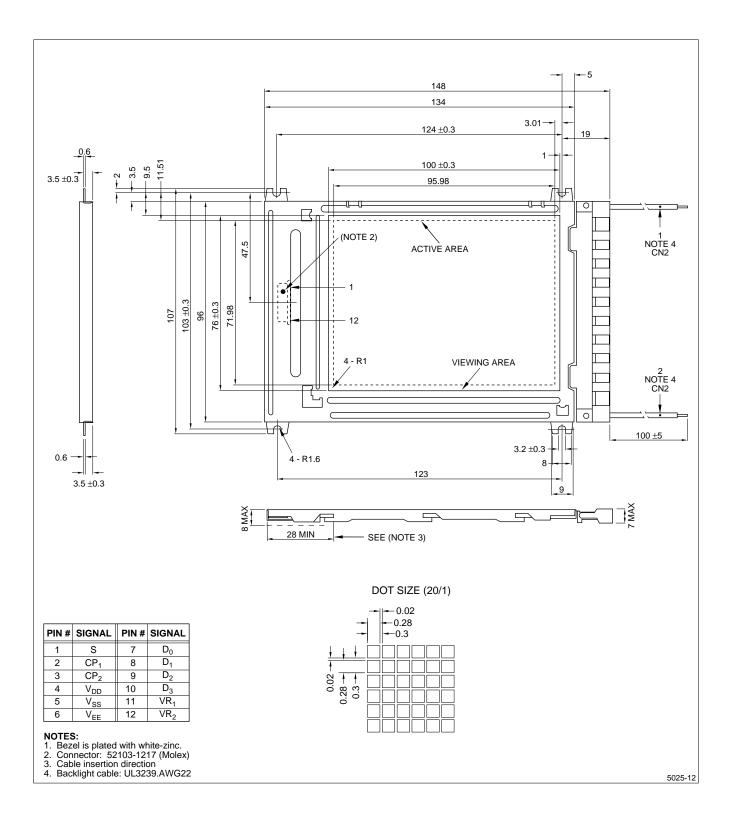

- Display Format: 320 × 240

- Overall Dimensions: 148 (W)  $\times$  96 (H)  $\times$  8 max (D) mm

- Active Area: 100 (W) × 76 (H) mm

- Dot Pitch: 0.28 (W) × 0.28 (H) mm

# DESCRIPTION

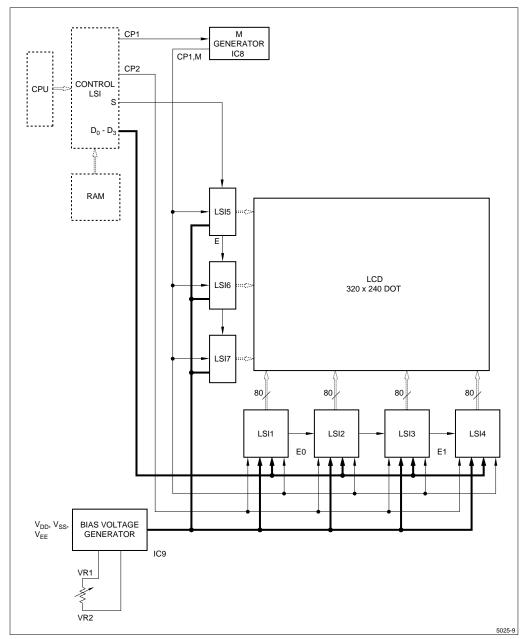

The SHARP LM32K10 Passive Matrix Color LCD consists of  $320 \times 240$  dots with a backlight system which uses a cold cathode fluorescent tube (CCFT). The LCD also consists of a DFSTN-type positive panel and a transflective viewing mode.

Figure 1. LM32K10 Block Diagram

#### **MECHANICAL SPECIFICATIONS**

| PARAMETER          | SPECIFICATIONS                             | UNIT | NOTE |

|--------------------|--------------------------------------------|------|------|

| Outline Dimensions | 148 (W) $\times$ 96 (H) $\times$ 8 max (D) | mm   | 1    |

| Active Area        | 100 (W) × 76 (H)                           | mm   | -    |

| Display Format     | 320 (W) $\times$ 240 (H) Full Dot          | Ι    |      |

| Dot Size           | 0.28 (W) × 0.28 (H)                        | mm   | _    |

| Dot Spacing        | 0.02                                       | mm   | _    |

| Base Color         | Black                                      | _    | 2, 3 |

| Background Color   | White                                      |      | 2    |

| Weight             | Approximately 140                          | g    | _    |

#### NOTES:

1. Excludes the mounting tab.

2. Due to the characteristics of the LC material, the colors vary with environmental temperature.

Negative-type display: Display data 'H': Dots ON: Black Display data 'L': Dots OFF: White

#### ABSOLUTE MAXIMUM RATINGS ( $t_A = 25^{\circ}C$ )

| SYMBOL                            | PARAMETER                  | MIN. | MAX.            | UNIT              |

|-----------------------------------|----------------------------|------|-----------------|-------------------|

| V <sub>DD</sub> – Vss             | Supply Voltage (Logic)     | 0    | 6.0             | V                 |

| V <sub>DD</sub> - V <sub>EE</sub> | Supply Voltage (LCD Drive) | 0    | 28.5            | V                 |

| V <sub>IN</sub>                   | Input Voltage              | 0    | V <sub>DD</sub> | V                 |

| VCCFT                             | Backlight                  | 0    | 1500            | V <sub>RMS</sub>  |

| ICCFT                             | Backlight                  | 0    | 6.5             | mA <sub>RMS</sub> |

#### **ENVIRONMENTAL CONDITIONS**

| ITEM                | TSTG  |       | TOPR |       | CONDITION               | NOTE |  |

|---------------------|-------|-------|------|-------|-------------------------|------|--|

|                     | MIN.  | MAX.  | MIN. | MAX.  |                         | NOTE |  |

| Ambient Temperature | −25°C | +60°C | 0°C  | +45°C | -                       | _    |  |

| Humidity            | -     |       | _    |       | No condensation         | 1    |  |

| Vibration           | -     | -     |      | _     | 3 Directions (X/Y/Z)    | 2    |  |

| Shock               | -     | _     |      | _     | 6 Directions (±X/±Y/±Z) | 3    |  |

NOTES:

1.  $t_A \leq 40^{\circ}C$ , 90% RH maximum.

$t_A > 40^{\circ}C$ , Absolute humidity less than  $t_A = 40^{\circ}C$  at 90% RH.

These test conditions are in accordance with IEC 68-2-6. Two hours for each direction of X/Y/Z (six hours total).

| Frequency       | 10 Hz to 55 Hz                   |

|-----------------|----------------------------------|

| Vibration Width | 1.5 mm                           |

| Interval        | 10 Hz to 55 Hz to 10 Hz/1.0 min. |

Acceleration: 490 m/s<sup>2</sup> (50 g) Pulse width: 11 ms Three times for each direction of ±X/±Y/±Z.

| SYMBOL                            | PARAMETER                     | MIN.         | TYP.     | MAX.            | UNIT              | NOTE                                                   |

|-----------------------------------|-------------------------------|--------------|----------|-----------------|-------------------|--------------------------------------------------------|

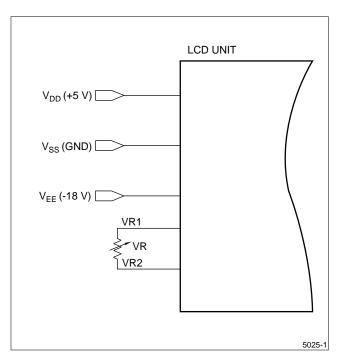

| V <sub>DD</sub> - V <sub>SS</sub> | Supply Voltage (Logic)        | 4.75         | 5.0      | 5.25            | V                 | -                                                      |

| $V_{\text{EE}} - V_{\text{SS}}$   | Supply Voltage<br>(LCD Drive) | -18.5        | -18.0    | -17.5           | V                 | V <sub>DD</sub> = 5.0 V<br>Note 1                      |

| V <sub>IN</sub>                   | Input Signal Voltage          | $0.8 V_{DD}$ | _        | V <sub>DD</sub> | V                 | 'H' Level                                              |

| V IN                              | input Signal Voltage          | 0            | _        | $0.2 V_{DD}$    | V                 | 'L' Level                                              |

| IIL                               | Input Leakage Current         | -            | _        | 20              | μΑ                | 'H' Level                                              |

| 11                                |                               | -20.0        | _        | _               | μA                | 'L' Level                                              |

| I <sub>DD</sub>                   | Supply Current (Logic)        | _            | T. B. D. | T. B. D.        | mA                | $V_{DD} = 5.0 V,$                                      |

| I <sub>EE</sub>                   | Supply Current (LCD)          | _            | T. B. D. | T. B. D.        | mA                | V <sub>EE</sub> = -18.0 V<br>V <sub>R</sub> = T. B. D. |

| P₀LCD                             | Power Consumption (LCD)       | _            | T. B. D. | T. B. D.        | mW                | F = 80 HZ                                              |

| V <sub>FTS</sub>                  | Start Voltage (B/L)           | _            | _        | 480             | V <sub>RMS</sub>  | La sutan                                               |

| V <sub>FTL</sub>                  | Supply Voltage (B/L)          | 225          | 250      | 275             | V <sub>RMS</sub>  | Inverter<br>LM000106                                   |

| I <sub>FT</sub>                   | Supply Current (B/L)          | 4            | 5        | 6               | mA <sub>RMS</sub> | Input Voltage 12 V                                     |

| Pdft                              | Power Consumption (B/L)       | _            | 1.25     | _               | W                 |                                                        |

# ELECTRICAL CHARACTERISTICS (t<sub>A</sub> = 25°C, V<sub>DD</sub> = 5.0 V $\pm$ 5%)

NOTE:

1. The viewing angle  $\theta$  obtains the maximum contrast by adjusting variable resistors between VR1 and VR2.

Figure 2. Display High Frequency Pattern

# INTERFACE SIGNALS

# CN1<sup>1</sup>

| PIN<br>NUMBER | SYMBOL          | PARAMETER                             | LEVEL           |

|---------------|-----------------|---------------------------------------|-----------------|

| 1             | S               | Scan Start-Up Signal                  | Н               |

| 2             | CP1             | Input Data Latch Signal               | $H\toL$         |

| 3             | CP2             | Data Input Clock Signal               | $H\toL$         |

| 4             | $V_{DD}$        | Power Supply For Logic and LCD (+5 V) | -               |

| 5             | V <sub>SS</sub> | Ground Potential (0 V)                | -               |

| 6             | VEE             | Power Supply for LCD (-18)            | _               |

| 7             | D <sub>0</sub>  |                                       |                 |

| 8             | D <sub>1</sub>  | Display Data Signal                   | H (ON), L (OFF) |

| 9             | D <sub>2</sub>  |                                       |                 |

| 10            | D <sub>3</sub>  |                                       |                 |

| 11            | VR1             | LCD Contrast Adjust (A)               | _               |

| 12            | VR2             | LCD Contrast Adjust (B)               | _               |

#### NOTE:

1. Connector used: 52103 - 1217 (Molex) Mating cable: 1.0 mm pitch, 12 pins F.F.C.

#### CN2

| PIN<br>NUMBER | SYMBOL | PARAMETER                       |

|---------------|--------|---------------------------------|

| 1             | VFT1   | Power Supply for CCFT Backlight |

| 2             | VFT2   | Power Supply for CCFT Backlight |

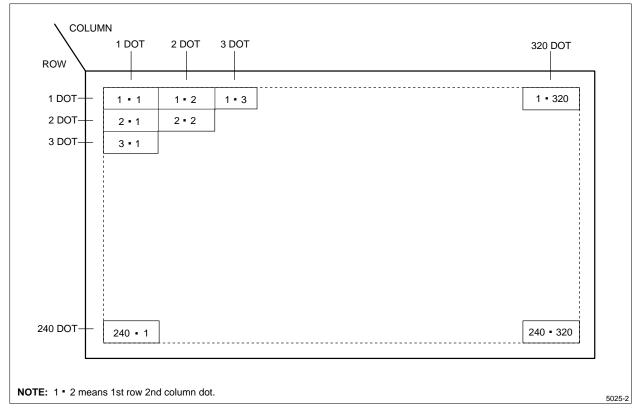

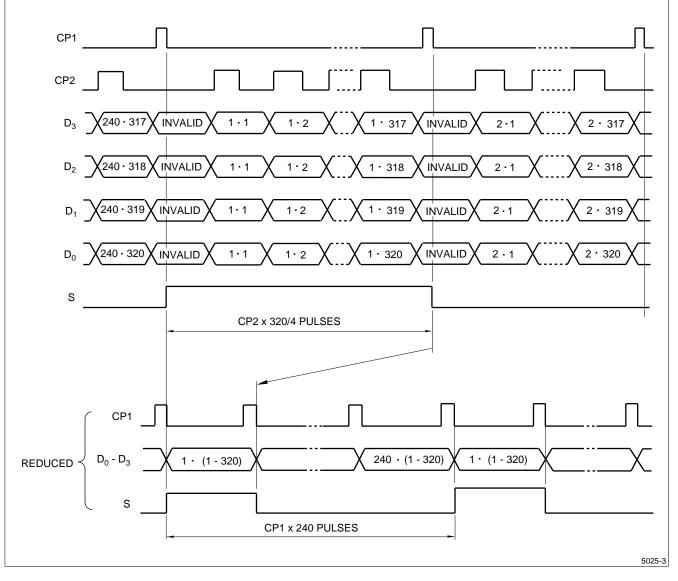

Figure 3. Dot Chart of Display Area

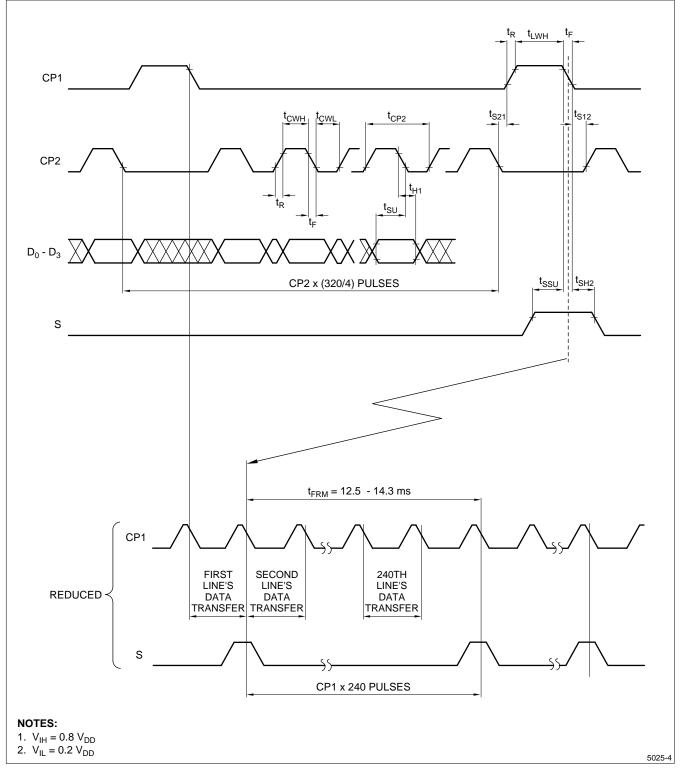

Figure 4. Data Input Timing

# INTERFACE TIMING RATINGS

| SYMBOL                          | PARAMETER                                                 | MIN. | TYP. | MAX. | UNITS |

|---------------------------------|-----------------------------------------------------------|------|------|------|-------|

| t <sub>FRM</sub>                | Frame Cycle                                               | 12.5 | _    | 14.3 | ms    |

| t <sub>CP2</sub>                | CP2 Clock Cycle                                           | 152  | _    | _    | ns    |

| tсwн                            | 'H' Level Clock Width                                     | 100  | _    | _    | ns    |

| t <sub>CWL</sub>                | 'L' Level Clock Width                                     | 100  | _    | _    | ns    |

| t <sub>LWH</sub>                | 'H' Level Latch Clock Width                               | 100  | _    | _    | ns    |

| tsu                             | Data Setup Time                                           | 80   | _    | _    | ns    |

| t <sub>HI</sub>                 | Data Hold Time                                            | 80   | _    | _    | ns    |

| t <sub>s12</sub>                | CP2 $\uparrow$ Clock Allowance Time From CP1 $\downarrow$ | 0    | _    | _    | ns    |

| t <sub>s21</sub>                | CP1 $\uparrow$ Clock Allowance Time From CP2 $\downarrow$ | 0    | -    | -    | ns    |

| t <sub>R</sub> , t <sub>F</sub> | Clock Rise/Fall Time                                      | _    | -    | 50   | ns    |

| t <sub>SSU</sub>                | S Signal Data Setup Time                                  | 100  | -    | _    | ns    |

| t <sub>SH2</sub>                | S Signal Data Hold Time                                   | 100  | _    | _    | ns    |

Figure 5. Interface Timing Chart

#### UNIT DRIVING METHOD

#### **Circuit Configuration**

Figure 1 shows the block diagram of the Unit's circuitry.

#### **Display Face Configuration**

The display face electrically consists of a signal display segment of  $320 \times 240$  dots.

#### Input Data and Control Signal

The LCD driver is 80 bits LSI, consisting of shift register, latch circuits, and LCD driver circuits.

Display data which is externally divided into data for each row (320 dots) is sequentially transferred in the form of 4-bit parallel data through shift registers by Clock Signal CP2 from the left top of the display face.

When data of one row (320 dots) has been input, they are latched in the form of parallel data for 320 lines of signal electrodes by Latch Signal CP1. Then the corresponding drive signal is transmitted to the 320 lines of column electrodes of the LCD panel by the LCD drive circuits.

At this time, scan start-up signal S is transferred from the scan signal driver to the first row of scan electrodes, and the contents of the data signals are displayed on the first row of the upper and lower half of the display face according in the combinations of voltages applied to the scan and signal electrodes of the LCD.

While the first rows of data are being displayed, the second rows of data are entered. When 320 dots of data have been transferred, then latched, on the falling edge of CP1 clock, the display face proceeds to the second rows of display.

Such data input is repeated up to the 240th row of each display segment, from upper to lower rows, to complete one frame of display using the time-sharing method. Then data input proceeds to the next display face.

Scan start-up signal S generates scan signal to drive horizontal electrodes. To avoid flickering, drive the unit at 70 - 80 Hz/frame.

Because of the characteristics of the CMOS driver LSI, the power consumption of the unit goes up as the operating frequency CP2 increases. Thus the driver LSI applies the system of transferring 4-bits parallel data through the four lines of shift registers to reduce the data transfer speed CP2. This system minimizes power consumption of the unit.

In this circuit configuration, 4-bit display data are input to data input pins of  $D_0 - D_3$ .

The LCD unit also adopts a bus line system for data input to minimize the power consumption. In this system, the data input terminal of each driver LSI is activated only when relevant data input is fed.

Data input for column electrodes of both the upper and the lower display segment and chip select of driver LSI are made as follows:

- The driver LSI at the left end of the display face is first selected, and the adjacent driver LSI of the right side is selected when 80 dots data (20 CP2) is fed. This process continues sequentially until data is fed to the driver LSI at the right end of the display face.

- This process is immediately followed at the column drivers LSI's of both the upper and the lower display segments. Thus, data input for both the upper and the lower display segments must be fed through 4-bit bus line sequentially from the left end of the display face.

Since this graphic display unit contains no refresh RAM, it requires data and timing pulse inputs even for static display.

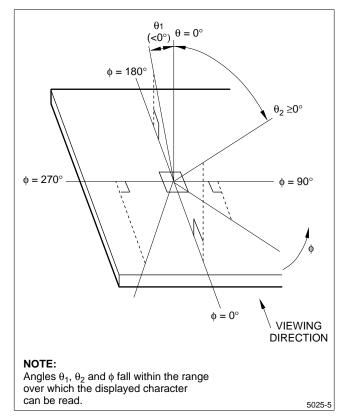

# OPTICAL CHARACTERISTICS ( $V_{DD} = 5.0 V$ , $t_A = 25^{\circ}C$ )

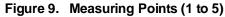

The following specifications show the optical characteristics when the viewing angle obtaining the maximum contrast ( $\phi$ ) is adjusted to 0 degrees.

| SYMBOL                                  | PARAMETER              | CONDITION                                                  |                      | MIN. | TYP. | MAX. | UNIT    | NOTE |

|-----------------------------------------|------------------------|------------------------------------------------------------|----------------------|------|------|------|---------|------|

| $\theta_2 - \theta_1$                   |                        | $\phi = 0^{\circ}$                                         | C <sub>0</sub> ≥ 2.0 | 60   | _    | _    |         |      |

| <b>θ</b> 1                              |                        |                                                            | $C_0 = 2.0$          | -    | _    | -30  |         |      |

| θ2                                      | Viewing Angle Range    | $\mathbf{\theta}_1 < \mathbf{\theta}_2$                    | $C_0 = 2.0$          | 25   | -    | -    | degrees | 1    |

| $\mathbf{\theta}_2 - \mathbf{\theta}_1$ |                        |                                                            | C <sub>0</sub> ≥ 2.0 | 65   | _    | _    |         |      |

| <b>θ</b> 1                              |                        | $ \phi = 90^{\circ} \\ \theta_1 < \theta_2 $               | $C_0 = 2.0$          | _    | _    | -35  |         |      |

| θ2                                      |                        |                                                            | $C_0 = 2.0$          | 25   | -    | _    |         |      |

| C <sub>0</sub>                          | Contrast Ratio         | $\mathbf{\Theta} = 0^{\circ}, \ \mathbf{\phi} = 0^{\circ}$ |                      | 8.0  | 10.0 | _    | _       | 2    |

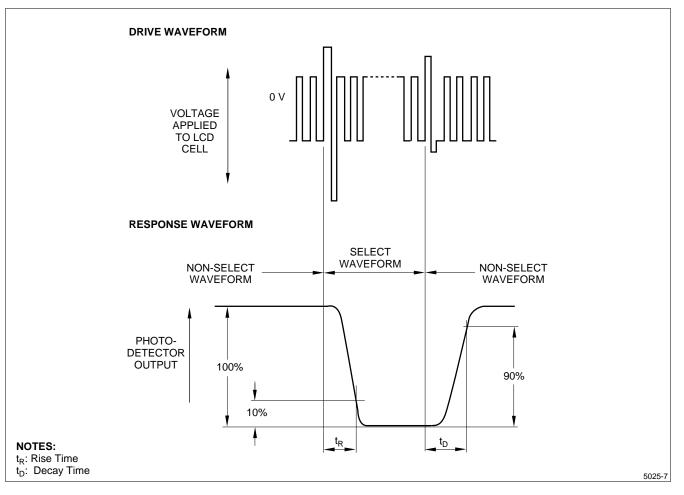

| t <sub>R</sub>                          | Response Speed – Rise  | $\mathbf{\Theta} = 0^{\circ},  \mathbf{\phi} = 0^{\circ}$  |                      | _    | 100  | 150  | ms      | 3    |

| t <sub>D</sub>                          | Response Speed – Decay | $\mathbf{\Theta} = 0^{\circ}$                              | $\phi = 0^{\circ}$   | _    | 150  | 200  | ms      | 5    |

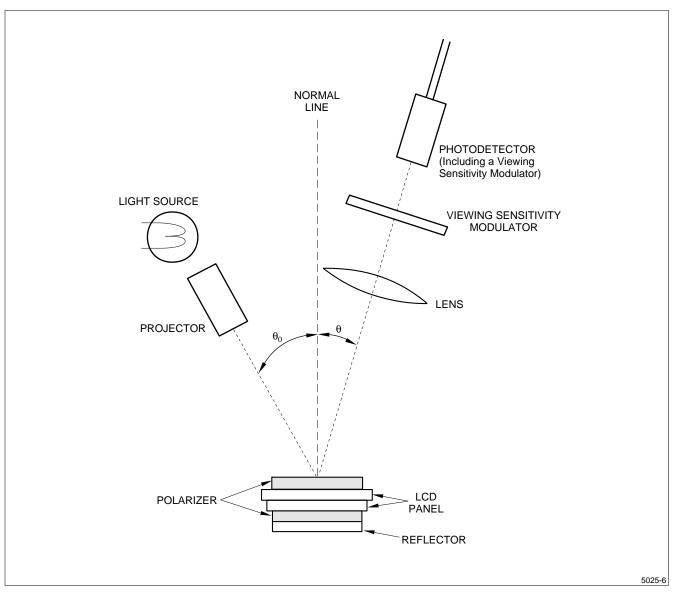

NOTES:

2. Contrast Ratio is defined as follows:

$C_0 = \frac{Photodetectoputputvoltage with non-select waveform being applied}{Photodetectoputputvoltage with non-select waveform being applied}$ Photodetectoroutput voltage with select waveformbeing applied

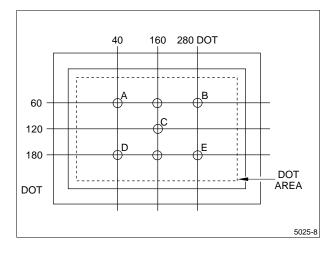

3. The response characteristics of photodetector output are measured as shown in Figure 7, assuming that input signals are applied to select and deselect the dots to be measured, in the optical characteristics test method shown in Figure 11.

Figure 6. Definition of Viewing Angle

<sup>1.</sup> The viewing angle is defined in Figure 6.

Figure 7. Optical Characteristics Test Method

Figure 8. Definition of Response Time

# CHARACTERISTICS OF BACKLIGHT

#### Brightness

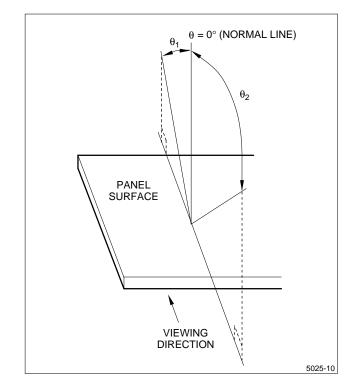

The ratings are defined as the average brightness at five measurement points.

| PARAMETER  | MIN.   | TYP.   | MAX. | UNIT              |

|------------|--------|--------|------|-------------------|

| Brightness | T.B.D. | T.B.D. | -    | cd/m <sup>2</sup> |

#### **Measurement Circuit**

CCFT Inverter:

LM000106

INPUT voltage: 12.0 V

$$IFT = 5 mA$$

LCD Unit Condition:

LCD is full dot OFF

$V_{EE} = -18.0 V$

Temperature:

$t_A = 25^{\circ}C$ , 30 minutes after turning on.

Measurement Equipment

BM-7 (TOPCON)

#### **Operating Life**

The operating lifetime is 10,000 hours or more under the following conditions:

• CCFT inverter is IFT = 5 mA RMs,  $t_A = 25^{\circ}C$ .

The operating lifetime is defined as having ended when any of the following conditions are met:

- When the illuminance or quantity of light has decreased to 50% of the initial value.

- When the CCFT flickers.

#### PRECAUTIONS

- Industrial (Mechanical) design of the product in which this LCD unit is incorporated must be so made that the viewing angle characteristics of the LCD are optimized. This unit's viewing angle is illustrated in Figure 10 and as follows:

- $\begin{array}{l} \ \theta_1 \ \text{min} < \text{viewing angle} < \theta_2 \ (\theta_1 < 0^\circ, \theta_2 \ge 0^\circ) \\ \text{Consider the optimum viewing conditions according to the purpose when installing the unit.} \end{array}$

Figure 10. Dot Matrix LCD Viewing Angle

This unit is installed using mounting tabs at the four corners of PCB or bezel. During installation, avoid undue stress on the unit such as twisting or bending. A transparent acrylic resin board or other type of protective panel should be attached to the front of the unit to protect the polarizer LCD cells, etc.

- Since the front polarizer is easily damaged, use care to not scratch the face.

- If the surface of the LCD cells need cleaning, wipe it with a soft cloth.

- Wipe liquid off immediately since it can cause color changes and staining.

- The LCD is made of glass plates. Use care when handling it to avoid breakage.

- This unit contains CMOS LSIs which are sensitive to electrostatic charges. The following measures should be taken to protect the unit from electrostatic discharge:

- Ground the metallic case of the main system (contact of the unit and main system).

- Insulate the unit and main system by attaching insulating washers made of bakelite or nylon.

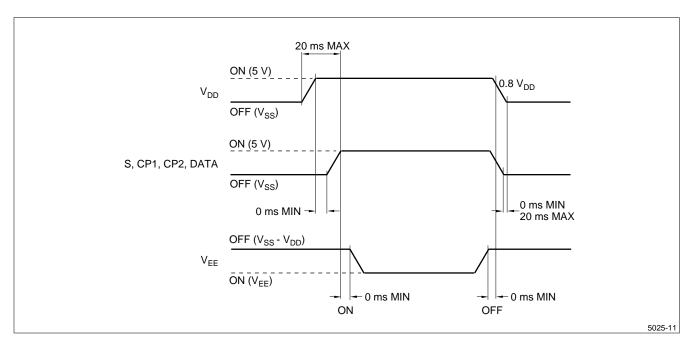

- The unit should be driven according to the specified ratings to avoid malfunction or permanent damage. DC voltage drive leads to rapid deterioration of LC, so ensure that the drive is alternating waveform by continuous application of the signal M. Avoid latch-up of driver LSIs and application of DC voltage to the LCD panel by following the ON/OFF sequence shown in Figure 11.

- Do not expose the unit to direct sunlight, strong ultraviolet light, etc., for prolonged periods.

- Store the unit at normal room temperature to prevent the LC from converting to liquid (due to excessive temperature changes).

- Do not disassemble the unit.

**WARNING:** Avoid using any materials which emit gas from epoxy resin (Amines' hardener) and silicon adhesive agent (dealcohol or deoxym) to prevent polarizer color change caused by gas.

Figure 11. Power ON/OFF Sequence

#### **OUTLINE DIMENSIONS**